Структура и многополевое применение однобитного полного сумматора

2024/7/29 15:10:14

Вид:

В компьютеризированном проектировании схем, одноразрядный полный сумматор представляет собой основной логический элемент схемы, который имеет два входных бита и вход для переноса, создавая целый выход и выход для переноса. Это важный компонент для создания многобитных сумматоров и других арифметических логических устройств. Одноразрядный полный сумматор может выполнять двоичное сложение и является одним из основных функциональных модулей, часто встречающихся в цифровых системах.

Определение

Одноразрядный полный сумматор представляет собой логическую схему с тремя входами и двумя выходами. Он принимает два входных бита данных (слагаемое и суммируемое) и сигнал переноса от предыдущего сложения, и выдает суммарный бит (Sum) и бит переноса (Carry Out). Полный сумматор можно рассматривать как логическую операцию с тремя входами и двумя выходами над двумя входными битами и битом переноса.

Одноразрядный полный сумматор обычно изображается в виде графического символа, включающего два входных бита (A и B), бит переноса (Cin), суммарный выходной бит (Sum) и выходной бит переноса (Carry Out).

Структура одноразрядного полного сумматора

Структура одноразрядного полного сумматора

Традиционная структура

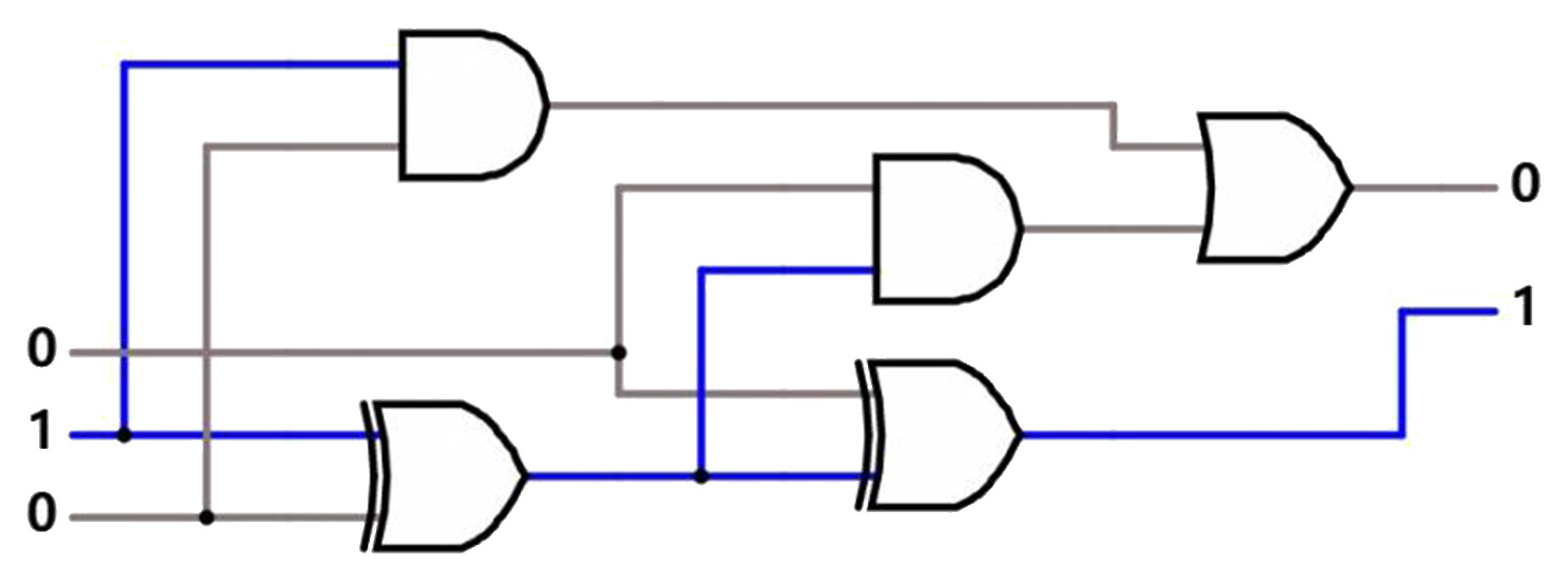

Одноразрядный полный сумматор часто состоит из основных логических элементов, таких как XOR, AND и OR. Обычная структура одноразрядного полного сумматора включает два элемента XOR, два элемента AND и один элемент OR для выполнения вышеупомянутых логических функций. Связь входов и выходов этих элементов позволяет одноразрядному полному сумматору правильно выполнять двоичное сложение.

Реализация

Одноразрядный полный сумматор может быть реализован непосредственно через логические элементы или с использованием интегральных схем (ИС) или языков программирования (например, Verilog, VHDL). В проектировании цифровых систем часто каскадируют несколько одноразрядных полных сумматоров для создания многобитных сумматоров, что позволяет выполнять сложение многобитных двоичных чисел.

Применения одноразрядного полного сумматора

Как основной элемент в проектировании цифровых схем, одноразрядный полный сумматор имеет широкое применение. Ниже приведены конкретные примеры применения:

Сумматоры и вычитатели

Одноразрядный полный сумматор часто используется в проектировании сумматоров и вычитателей. Каскадируя несколько одноразрядных полных сумматоров, можно создать многобитные двоичные сумматоры и вычитатели для выполнения операций сложения и вычитания чисел.

Процессоры

В арифметико-логическом устройстве (ALU) компьютера одноразрядный полный сумматор используется для выполнения операций сложения, вычитания и логических операций. ALU является одним из основных компонентов, отвечающих за выполнение арифметических и логических операций в компьютере.

Цепи управления временем

Одноразрядный полный сумматор может использоваться в цепях управления временем, таких как часы и делители частоты. Он помогает достичь точных функций управления временем, обеспечивая стабильность цифровых систем.

Кодировщики

В цифровых дисплейных устройствах, таких как семисегментные дисплеи и светодиодные экраны, одноразрядный полный сумматор используется для преобразования двоичных чисел в соответствующие цифровые сигналы для отображения.

Криптография и информационная безопасность

В шифровании и дешифровании данных одноразрядный полный сумматор и его каскадная структура широко используются в проектировании алгоритмов шифрования данных и систем связи для обеспечения безопасности данных.

Нейронные сети

В области искусственного интеллекта одноразрядный полный сумматор можно использовать для создания слоев взвешенных сумм в нейронных сетях, помогая выполнять задачи, такие как распознавание образов и глубокое обучение.

Обработка данных датчиков

В встраиваемых системах и устройствах IoT одноразрядный полный сумматор можно использовать для обработки данных с датчиков, выполнения логики управления и реализации интеллектуальной обработки данных и принятия решений.

Высокопроизводительные вычисления

В суперкомпьютерах и системах высокопроизводительных вычислений одноразрядный полный сумматор широко используется для обработки данных в большом масштабе, научных вычислений и задач моделирования, обеспечивая мощную вычислительную поддержку.