Стратегия оптимизации параметров FPGA VREF

2024/7/23 17:07:15

Вид:

Метод оптимизации схемы генерации VREF

Чтобы улучшить производительность интерфейса SelectIO FPGA, можно рассмотреть следующие аспекты:

1. Выбор подходящего источника VREF: В проектировании FPGA VREF обычно генерируется с помощью внешних источников питания, внутренних регуляторов или делителей напряжения. Каждый источник VREF имеет свои характеристики и подходящие сценарии использования. Поэтому важно выбирать подходящий источник VREF, исходя из конкретных требований приложения и аппаратных условий.

2. Разработка фильтрующей схемы: Интерфейс SelectIO FPGA может быть подвержен шумовым помехам из внешней среды. Поэтому важно разработать подходящую фильтрующую схему в цепи генерации VREF. Правильные фильтрующие схемы могут эффективно подавлять шумовые помехи и повышать стабильность VREF. Общие типы фильтрующих схем включают RC-фильтры и LC-фильтры, которые широко используются в различных приложениях для обеспечения чистоты и стабильности сигнала.

3. Оптимизация разводки и трассировки на печатной плате: Разводка и трассировка на печатной плате значительно влияют на стабильность VREF. Схема генерации VREF должна быть размещена рядом с FPGA и использовать короткие и широкие дорожки для уменьшения шумовых помех. Кроме того, следует уделять внимание изоляции и экранированию от других сигнальных линий.

4. Написание кода на Verilog HDL для управления: Путем написания кода на Verilog HDL можно достичь точного управления схемой генерации VREF. Например, изменение выходного напряжения внутреннего регулятора или коэффициента деления делителя резисторов может точно контролировать значение VREF. Кроме того, значение VREF может контролироваться в режиме реального времени и при необходимости корректироваться для обеспечения его стабильности.

Важность схемы генерации VREF

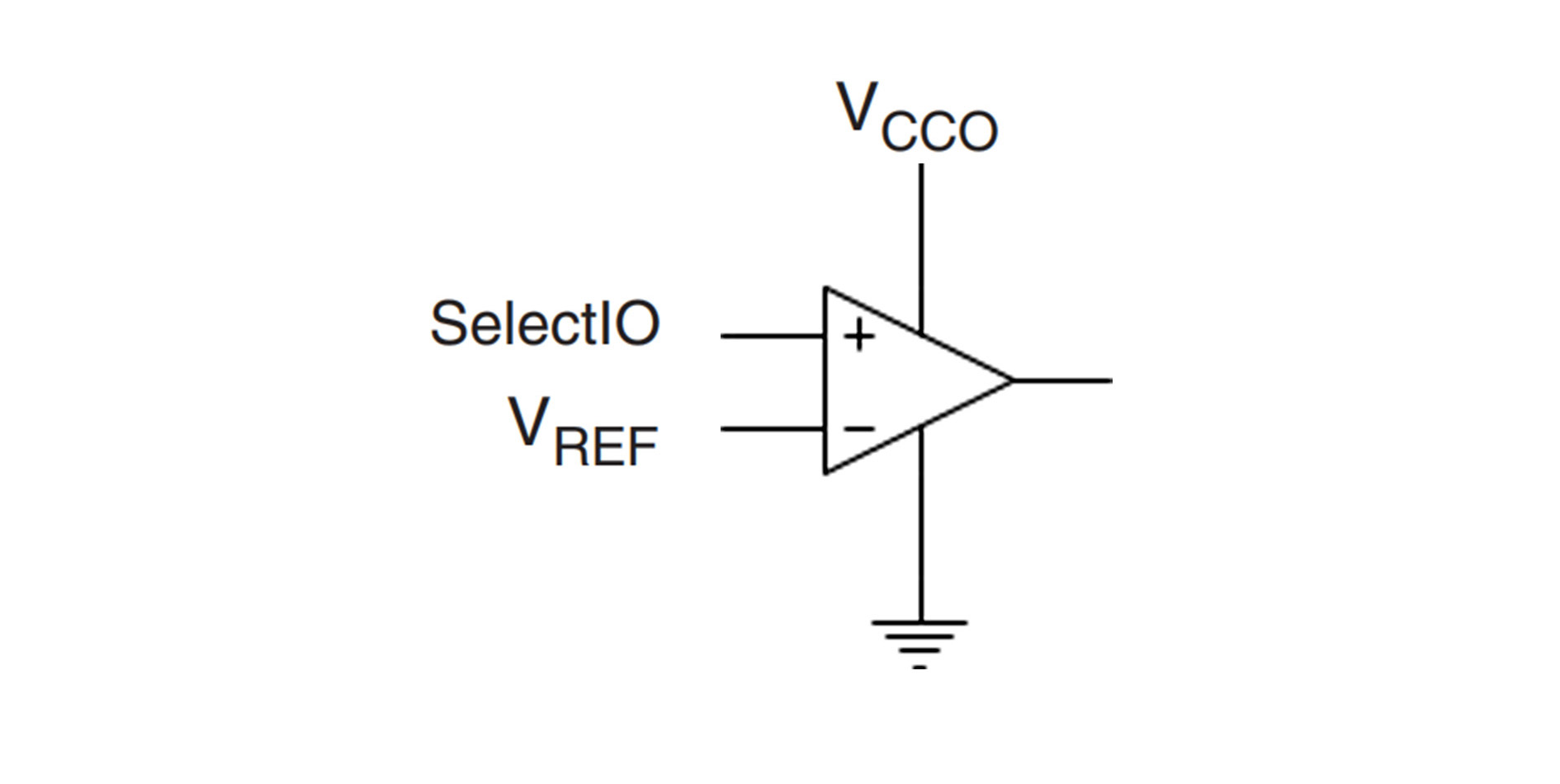

В интерфейсе SelectIO FPGA VREF является важным параметром, определяющим диапазон напряжений интерфейса и точность согласования. Подходящее значение VREF обеспечивает согласование напряжений между интерфейсом и периферийными устройствами, уменьшая отражение и искажение сигнала, что улучшает качество передачи сигнала. Кроме того, VREF значительно влияет на способность интерфейса подавлять шум и контролировать энергопотребление. Стабильное значение VREF может эффективно подавлять шумовые помехи в интерфейсе, улучшать отношение сигнал/шум и точно контролировать энергопотребление интерфейса путем регулировки значения VREF, что, в свою очередь, снижает общее энергопотребление системы.

Пример кода на Verilog HDL

Ниже приведен простой пример кода на Verilog HDL для генерации стабильного значения VREF в FPGA:

```verilog

module VREF_Generator(

input wire clk, // Тактовый сигнал

input wire rst_n, // Сигнал сброса

output reg vreg_out // Генерируемый выход VREF

);

const int vreg_target = 1200; // Предположим, что целевое значение VREF равно 1.2В (в мВ)

reg [11:0] vreg_current = 0; // Предположим, что используется 12-битная точность для представления значения VREF (0-4095 соответствует 0-VREF_MAX)

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

vreg_current <= vreg_target >> 12; // Установка начального значения VREF при сбросе

end else begin

// Корректировка значения vreg_current на основе какого-либо алгоритма или условия в каждом тактовом цикле

// В реальном применении необходимо корректировать в зависимости от конкретных условий

end

end

assign vreg_out = vreg_current / 4095.0 * VREF_MAX; // Предположим, что VREF_MAX - это максимальное доступное значение напряжения VREF

endmodule

Оптимизация схемы генерации VREF интерфейса SelectIO FPGA: проектирование и реализация

Эта статья подробно расскажет о том, как оптимизировать схему генерации VREF интерфейса SelectIO FPGA для повышения производительности и стабильности интерфейса, а также приведет соответствующие примеры кода на Verilog HDL.

Надеемся, что данное введение предоставит читателям некоторые идеи и методы для оптимизации схемы генерации VREF интерфейса SelectIO FPGA для применения и улучшения в реальном проектировании.

Обратите внимание, что приведенный выше код является лишь простым примером, иллюстрирующим, как генерировать стабильное значение VREF в FPGA. В реальных приложениях необходимо вносить корректировки и оптимизации в зависимости от конкретных аппаратных условий и требований приложения.