Улучшение временного анализа VLSI с помощью статического временного анализа

2022/10/29 10:46:15

Вид:

В мире проектирования Исключительно Широкомасштабной Интеграции (VLSI) точный анализ времени играет ключевую роль в обеспечении работоспособности, производительности и надежности интегральных схем. По мере уменьшения масштаба технологий и увеличения сложности проверка временных характеристик становится все более сложной задачей. Проверенная методика для решения этих задач - Статический Тайминг Анализ (STA), мощная техника, используемая для проверки времени в VLSI-проектах. В этой статье рассматривается, как STA улучшает тайминг-анализ VLSI, предлагая понимание методики, применения и преимуществ.

Операционные усилители, Часть 1: ОпАмп LM324N Компаратор

Оглавление

- Что такое Статический Тайминг Анализ?

- Основные концепции Статического Тайминг Анализа

- Как STA улучшает тайминг-анализ VLSI

- Пример использования STA в VLSI

- Реальное синхронизирование часов в тайминге VLSI

- Проблемы в Статическом Тайминг Анализе

- Примеры использования STA в промышленности

- Заключение

- Часто задаваемые вопросы

Что такое Статический Тайминг Анализ?

Статический Тайминг Анализ (STA) - это метод, используемый при проектировании и проверке цифровых схем для прогнозирования, будет ли проект соответствовать временным ограничениям без симуляции всего поведения схемы. Вместо выполнения динамической симуляции STA проверяет все возможные пути в цепи, чтобы убедиться, что сигналы приходят в нужные точки в пределах заданных временных интервалов.

В отличие от динамических симуляций, которые требуют входных векторов, STA оценивает временные характеристики цепи, вычисляя задержки распространения сигналов по различным путям. Он гарантирует, что сигналы не нарушают требований к установке и удержанию, предлагая более эффективный способ проверки времени работы цепи, чем методы исчерпывающей симуляции.

Основные концепции Статического Тайминг Анализа

Прежде чем углубиться в воздействие STA на тайминг-анализ VLSI, важно понять несколько ключевых концепций, связанных с STA.

Время установки и удержания

Одна из главных целей STA - это обеспечение соблюдения времени установки и удержания. Время установки относится к минимальному времени до фронта тактового сигнала, в течение которого сигнал данных должен оставаться стабильным, а время удержания - это время после фронта тактового сигнала, в течение которого сигнал должен оставаться стабильным. Нарушение этих времен может привести к неисправностям схемы.

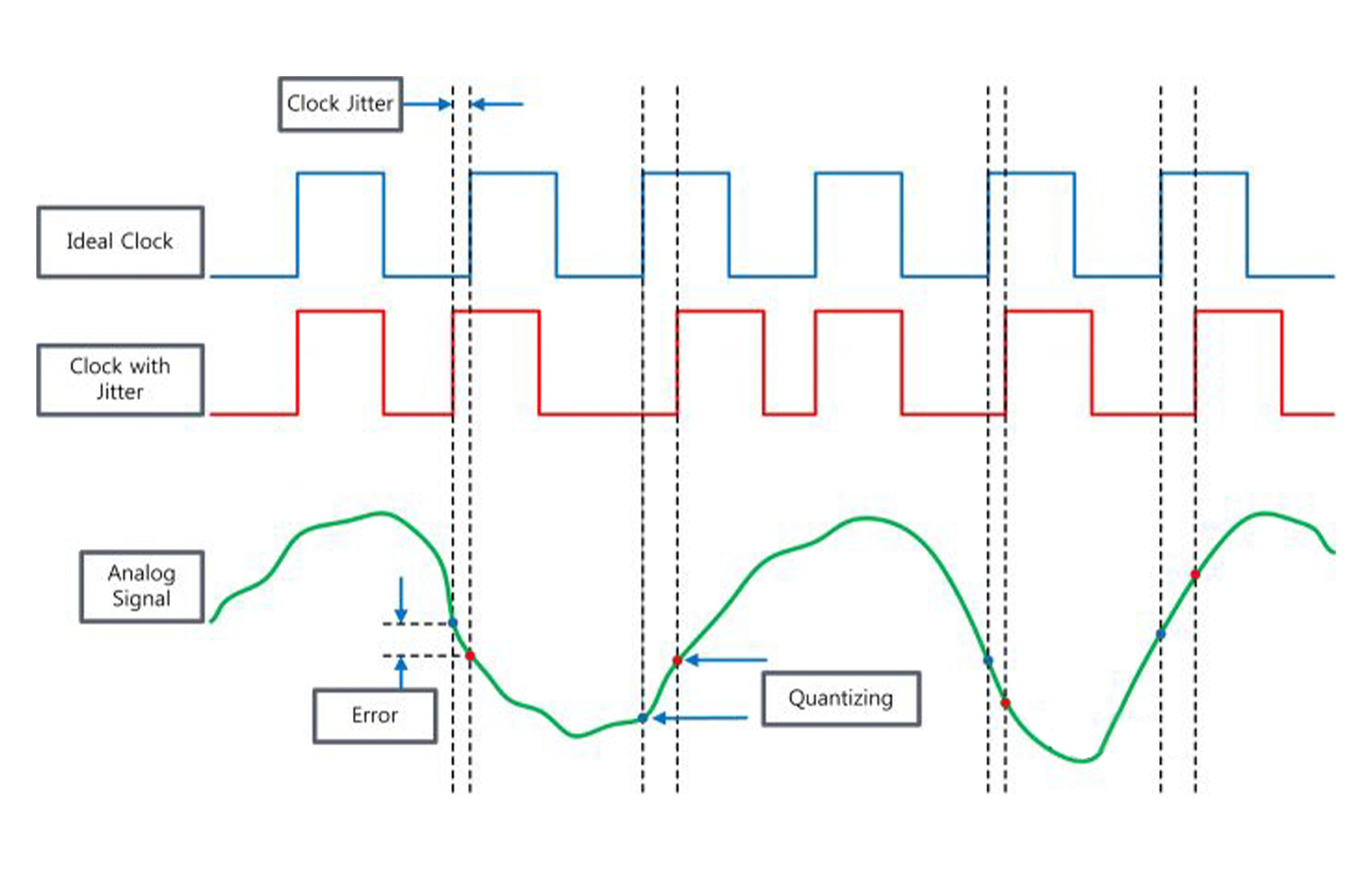

Сдвиг тактового сигнала

Сдвиг тактового сигнала - это разница во времени между приходом тактовых сигналов в разные части схемы. Чрезмерный сдвиг может привести к нарушениям времени, и STA играет ключевую роль в обнаружении и устранении проблем со сдвигом тактового сигнала в проектах VLSI.

Временные пути

В любой цифровой схеме существует несколько путей между триггерами и логическими элементами, по которым может передаваться сигнал. STA анализирует время этих путей, чтобы убедиться, что сигналы проходят в пределах заданных временных интервалов, обеспечивая работу схемы на заданной частоте.

Пример временных путей

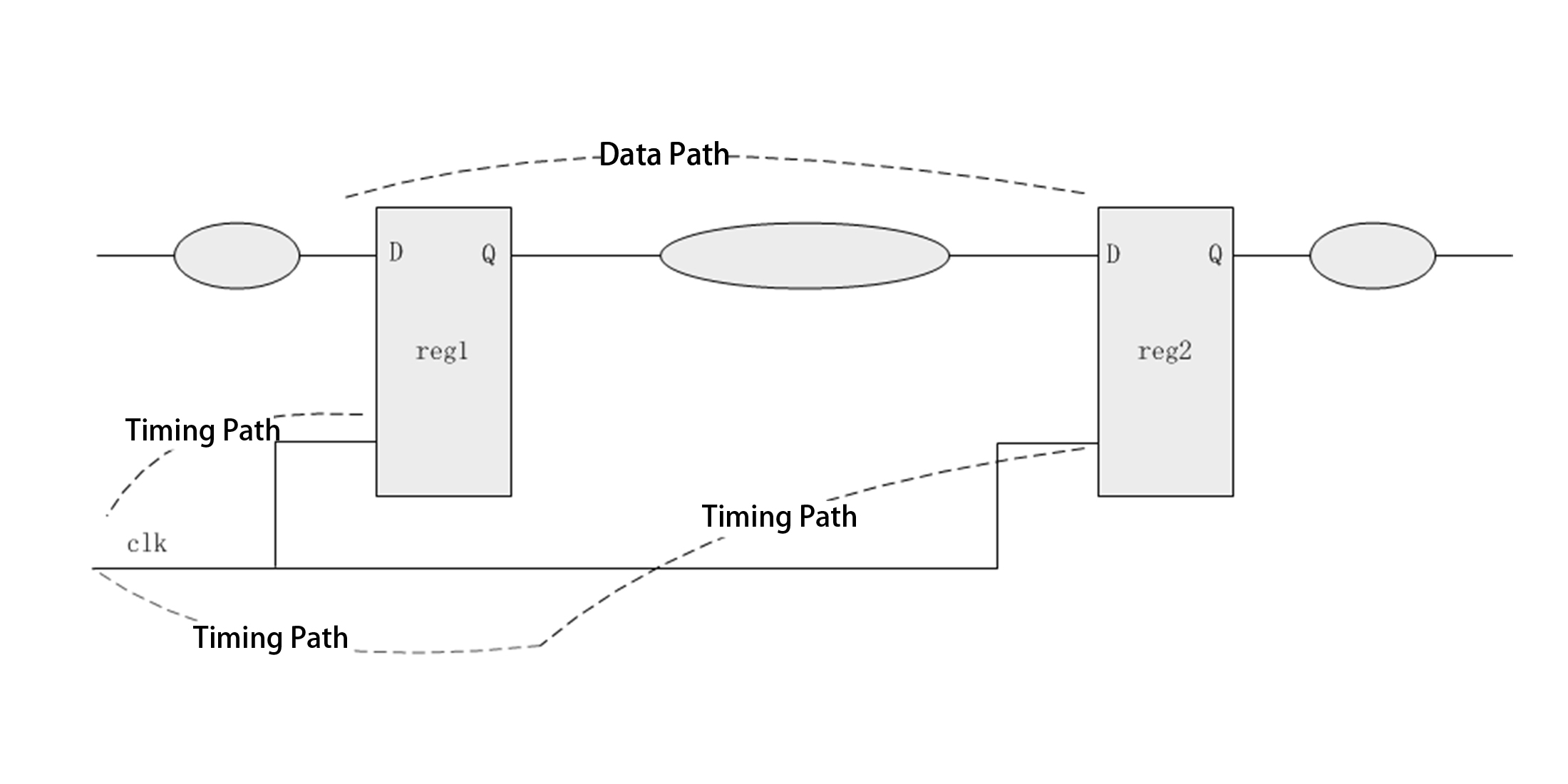

На диаграмме ниже представлен пример временного пути между двумя регистрами (reg1 и reg2). Сигнал распространяется от reg1 к reg2 через комбинированную логику на пути данных, в то время как временной путь проверяет, соответствует ли сигнал требованиям к установке и удержанию относительно тактового сигнала (clk).

Концепции времени

Как STA улучшает тайминг-анализ VLSI

1. Всеобъемлющий охват всех путей

Одним из самых значительных преимуществ STA является то, что он анализирует все возможные пути в цепи, как критические, так и некритические. Этот всеобъемлющий охват гарантирует, что ни одно нарушение времени не будет упущено, что повышает уверенность в производительности проекта. В отличие от методов динамической симуляции, которые анализируют пути на основе предоставленных входных векторов, STA может упустить важные временные нарушения.

2. Скорость и эффективность

STA является более быстрым и эффективным подходом к анализу времени по сравнению с динамическими симуляциями. Поскольку STA не требует входных векторов, он может быстро оценить временные характеристики цепи без необходимости выполнения множества симуляций. Эта скорость особенно полезна для крупномасштабных VLSI-проектов с миллионами транзисторов.

3. Раннее обнаружение нарушений времени

Используя STA на ранних этапах проектирования, инженеры могут выявлять и устранять потенциальные нарушения времени до того, как они станут дорогостоящими и сложными для исправления на поздних этапах. Раннее обнаружение повышает общую надежность проекта, снижая риск функциональных сбоев.

4. Применение к нескольким тактовым сигналам

Современные проекты VLSI часто включают сложные схемы с несколькими тактовыми сигналами, работающими на разных частотах. STA весьма эффективен в анализе временных путей, связанных с несколькими тактовыми сигналами и доменами, выявляя такие проблемы, как сдвиг тактового сигнала и нарушения при пересечении тактовых доменов.

5. Определение критических путей

STA идентифицирует критические пути в проекте, которые определяют максимальную рабочую частоту цепи. Зная, какие пути являются критическими, разработчики могут оптимизировать их для повышения общей производительности схемы. Эта оптимизация приводит к более быстрым проектам, что позволяет использовать более высокие тактовые частоты и повышать эффективность.

Преимущества STA

Пример использования STA в VLSI

Чтобы лучше понять роль STA в VLSI, рассмотрим пример цифровой цепи с блоками комбинационной логики, соединенными между двумя триггерами. Сигналы передаются от одного триггера к другому через комбинационную логику, и STA оценивает задержку распространения по этому пути.

В этом случае STA в VLSI гарантирует, что сигнал достигает конечного триггера до следующего фронта тактового сигнала, и проверяет, соблюдаются ли времена установки и удержания. Если обнаружено нарушение времени, STA может точно указать местоположение и проблему, что позволяет разработчику изменить путь или тактовые ограничения.

Типы путей и их влияние

Реальное синхронизирование часов в тайминге VLSI

Точное синхронизирование тактовых сигналов важно для высокопроизводительных цифровых систем. Одним из ключевых аспектов анализа времени работы схем является обеспечение точной синхронизации тактовых сигналов между несколькими компонентами и системами. Современные системы используют анализаторы реального времени для обеспечения точной синхронизации времени по всей цепи.

Использование NTP-синхронизации

Протокол сетевого времени (NTP) часто используется для синхронизации тактовых сигналов в распределенных системах. Синхронизация NTP позволяет системе поддерживать согласованное время между различными компонентами, обеспечивая отсутствие сдвига или задержек в тактовых сигналах. Это особенно важно в VLSI-проектах, использующих высокоскоростные протоколы связи, где точное время имеет решающее значение.

Используя синхронизацию сетевого времени, разработчики VLSI могут минимизировать риски, связанные с пересечением тактовых доменов и нарушениями тайминга, которые могут возникнуть из-за асинхронных тактовых сигналов. Решения по синхронизации NTP гарантируют, что все части системы работают синхронно, снижая вероятность ошибок времени.

Синхронизация тактовых сигналов для повышения точности времени

Синхронизация тактовых сигналов по всей цепи важна для надежной передачи и обработки данных. Синхронизированные тактовые сигналы помогают обеспечить выполнение всех временных требований, особенно в системах с несколькими тактовыми доменами. STA работает в тандеме с методами синхронизации тактовых сигналов для повышения надежности тайминга в VLSI-проектах.

Сравнение методов синхронизации часов

Проблемы в Статическом Тайминг Анализе

Несмотря на многочисленные преимущества, STA имеет свои трудности. Некоторые из распространенных проблем, с которыми сталкиваются при STA в тайминг-анализе VLSI, включают:

1. Обработка нескольких тактовых доменов

Во многих VLSI-проектах присутствуют несколько тактовых доменов, работающих на разных частотах. Обеспечение правильного времени работы между этими доменами может быть сложной задачей, поскольку пересечение тактовых доменов может вызвать потенциальные нарушения времени. STA помогает смягчить эти проблемы, но требует тщательного проектирования и стратегий синхронизации тактовых сигналов.

2. Моделирование технологических вариаций

По мере уменьшения технологических процессов влияние технологических вариаций на время работы становится более заметным. Вариации напряжения, температуры и технологических процессов могут значительно влиять на временное поведение, и STA должен учитывать эти вариации для предоставления точных результатов анализа.

3. Учет условий окружающей среды

Временные характеристики могут изменяться в различных условиях окружающей среды, таких как температурные и напряженческие вариации. STA должен учитывать наихудшие сценарии, чтобы гарантировать правильность времени работы в любых условиях эксплуатации, что усложняет анализ.

4. Нелинейное поведение цепей

Некоторые цепи демонстрируют нелинейное поведение, которое может быть сложно точно моделировать с помощью инструментов STA. В таких случаях разработчикам может потребоваться дополнить STA дополнительными методами симуляции для проверки временной производительности.

Проблемы STA

Примеры использования STA в промышленности

STA широко используется в полупроводниковой промышленности для проектирования и проверки различных типов схем, включая микропроцессоры, цифровые сигнальные процессоры (DSP) и модули памяти. Некоторые распространенные примеры использования статического тайминг анализа в реальных приложениях включают:

Проектирование микропроцессоров: Обеспечение соответствия критических путей микропроцессора временным требованиям для достижения требуемой тактовой частоты.

Проектирование памяти: Проверка выполнения временных ограничений на чтение и запись в модулях памяти.

DSP и GPU: Проверка времени по путям данных и управляющим сигналам для обеспечения высокопроизводительных вычислений.

Заключение

В области проектирования VLSI Статический Тайминг Анализ является важным инструментом для обеспечения соответствия цепи временным требованиям. Анализируя временные пути, выявляя потенциальные нарушения на ранней стадии и оптимизируя критические пути, STA играет ключевую роль в повышении производительности и надежности систем VLSI. Кроме того, использование инструментов для анализа реального времени, протоколов синхронизации NTP и инструментов синхронизации часов обеспечивает точность времени во всех доменах и компонентах, что позволяет поддерживать бесперебойную работу сложных цифровых схем.

По мере развития технологий STA останется основой проектирования VLSI, помогая инженерам соответствовать постоянно растущим требованиям к более быстрым, более надежным и более эффективным интегрированным схемам. С прогрессом в инструментах и методах STA будущее анализа времени работы VLSI выглядит многообещающим, предлагая более точные и эффективные решения для проблем современного проектирования цепей.